VNU Journal of Science: Computer Science and Communication Engineering

Journal homepage: http://www.jcsce.vnu.edu.vn/index.php/jcsce

# An Adaptive and Wide-Range Output DC-DC Converter for Loading Circuit of Li-Ion Battery Charger

## Nguyen Van Hao, Nguyen Duc Minh, Pham Nguyen Thanh Loan<sup>\*</sup>

BKIC Lab, School of Electronics and Telecommunications, Hanoi University of Science and Technology, Hanoi, Vietnam

## Abstract

In this paper, an adaptive and wide-range output DC-DC converter designed for lithium-ion (Li-Ion) battery charger circuit is proposed. The converter operates in continuous conduction mode (CCM) to provide an output voltage in response to battery voltage and a wide-range output current to ensure that circuit requirements are met. This circuit is designed on Cadence using 0.35-µm BCD technology. Simulation results show that the circuit fully operates in CCM mode with a load current from 50 mA to 1000 mA and output voltage ripple factor is less than 1 %. Furthermore, the current supplied to the load circuit responses to three types of Li-Ion rechargeable currents. The output voltage of the converter varies from 2.8 to 4.5 V corresponding to the voltage range of the battery being charged from 2.5 to 4.2 V. The average power efficiency of the converter in large load current mode (1000 mA) reaches 94 %.

Received 12 April 2018, Revised 18 June 2018, Accepted 18 June 2018

Keywords: Li-Ion battery, charging mode, charger circuit, DC-DC converter, adaptive reference voltage.

## 1. Introduction

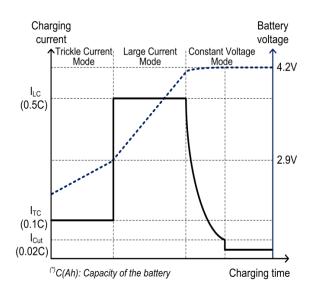

Today, Li-Ion batteries are widely used in consumer electronics for its significant advantages such as high energy density, high recharge cycle (> 1000 cycles), no memory effect, low self-discharged rate (2 - 8 % per month), wide range of operating condition (charge at -20 - 60 °C, discharge at -40 - 65 °C). In addition, a single cell of Li-Ion battery can operate in the range of 2.5 to 4.2 V [1]. The charging circuit is designed according to three modes following the charging standard [2, 3] as

shown in figure 1. Trickle constant current mode (TC) occurs when the battery voltage is less than 2.9 V, large constant current mode (LC) when the battery voltage is in the range of 2.9 to 4.2 V, and constant voltage charging mode (CV) when the battery voltage reaches 4.2 V.

In [4-6], the charging circuit is designed based on the structure of a low dropout regulator which offers high integration, fast and accurate control. But this charging structure has low power efficiency due to large deviation between supply voltage and battery voltage. To overcome this drawback, some techniques were proposed and presented in [7, 8].

<sup>\*</sup> Corresponding author. loan.phamnguyenthanh@hust.edu.vn https://doi.org/10.25073/2588-1086/vnucsce.194

Figure 1. Li-Ion battery charging modes.

switching mode The power supply converter is used to generate a variable supply voltage changing in response to the battery voltage during the charging process. However, the use of large off-chip elements for the boost converter structure in [7] and the flyback converter in [8] increase the size of printed circuit board (PCB). The rechargeable circuit in [9, 10] adopted the buck converter structure minimizing the size of PCB. However, the TC charging mode was not introduced and there was no isolation between DC-DC converter and battery so the self-discharge of battery may occur and battery performance cannot be guaranteed. In this article, we propose an adaptive buck DC-DC converter based on a buck converter structure that operates in continuous conduction mode (CCM) with a wide range of voltage and current variations in accordance with the Li-Ion charging circuit that was presented in our previous work [11].

The rest of the paper is structured as follows: Section 2 describes the structure of an adaptive and wide-range output DC-DC converter with a battery charger as load. Design parameters are considered and calculated in Sub-Section 2 to ensure that the converter operates stably in CCM mode and can supply a wide range of voltage and current to the load circuit. In Section 3, the simulation results are shown to evaluate the converter's performance. Finally, the conclusion is given in Section 4.

## 2. Circuit descriptions

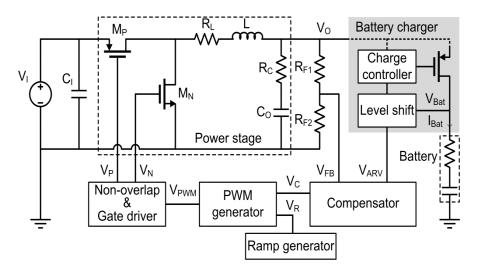

In general, the PWM DC-DC converter, as shown in figure 2, is implemented to provide a stable output voltage Vo from the input voltage V<sub>I</sub> thanks to the closed loop control. The feedback voltage V<sub>FB</sub> is sampled from the output through a voltage divider of two resistors  $R_{F1}$ ,  $R_{F2}$ . In the compensator, the  $V_{FB}$  will be compared with the reference voltage  $V_{ARV}$  to generate the deviation voltage V<sub>C</sub> which is used to determine the duty cycle of  $V_{PWM}$  from the PWM generator circuit. The switching signals  $V_N$ ,  $V_P$  to the gate of two power MOSFET N and P are finally generated by the non-overlap gate driver. The output filter LC<sub>0</sub> is well chosen to stabilize the output voltage that can be determined as follows (1)

$$V_{O} = \left(\frac{R_{F1} + R_{F2}}{R_{F2}}\right) V_{ARV}$$

(1)

Besides, the load of this DC-DC converter is a Li-Ion battery charging circuit which has been implemented in [11]. In that previous work, the varying battery voltage V<sub>Bat</sub> during the charging process is fed into the voltage level-shift circuit to provide a variable reference voltage V<sub>ARV</sub>, which is also called an adaptive reference voltage. The DC-DC converter's output voltage Vo should also be controlled to follow the battery voltage  $V_{Bat}$  so that the power efficiency of the whole system is improved. In this design, the value of the input voltage  $V_I$  is. around 6 V, switching frequency  $F_{SW}$  is selected at 500 KHz and the output voltage  $V_0$  of the converter is expected to be always 0.3 V higher than the battery voltage  $V_{Bat}$ .

Figure 2. Structure of adaptive DC-DC converter with Li-Ion battery charger as load.

#### 2.1. Compensator

То ensure the current and voltage requirements to the load circuit, the analysis of a conventional buck converter presented in [12] is employed to determine the value of inductor L and the ceramic capacitor Co. The theoretical calculation pointed out that the corresponding values of inductor and capacitor should be 22  $\mu$ H (R<sub>L</sub>  $\approx$  46 m $\Omega$ ) and 22  $\mu$ F (R<sub>C</sub>  $\approx$  5 m $\Omega$ ) respectively. The transfer function of power converter stage is thus defined as a function of double-pole  $\omega_{LC}$  (7.23 KHz) generated by the  $LC_0$  filter and one zero  $\omega_{ESR}$  (1.45 MHz) created by the equivalent series resistance R<sub>C</sub> and C<sub>0</sub>. To stabilize the circuit and compensate the phase degradation caused by the doublepole, the type-III compensation is adopted as shown in figure 3. Error amplifier EA is designed using a class AB two-stage op-amps with high and symmetrical slew rate [13]. Transfer function of the compensation circuit given in (2) consists of three poles ( $\omega_{P0}$ ,  $\omega_{P1}$ ,  $\omega_{P2}$ ) and two zeros ( $\omega_{Z1}$ ,  $\omega_{Z2}$ ). The zero frequency  $\omega_{\text{ESR}}$  is much larger than the switching frequency  $\omega_{sw}$  so that it does not affect the frequency range of the converter. In this approach, zero frequencies  $\omega_{Z1}$  and  $\omega_{Z2}$  are

designed in adjacent to the double-pole at frequencies  $0.6\omega_{LC}$  and  $1.5\omega_{LC}$  respectively. Pole frequency  $\omega_{P1}$  is set at  $0.5\omega_{SW}$  and  $\omega_{P2}$  is calibrated in frequency range of  $(0.8 - 0.9)\omega_{SW}$ .

$$K_{C}(s) = \frac{1}{R_{FI}(C_{2}+C_{3})} \frac{1}{s} \frac{\left(1+\frac{s}{\omega_{ZI}}\right)\left(1+\frac{s}{\omega_{Z2}}\right)}{\left(1+\frac{s}{\omega_{P2}}\right)} \quad (2)$$

With,

$$\omega_{P0} = 0, \quad \omega_{PI} = \frac{1}{R_{1}C_{1}}, \quad \omega_{P2} = \frac{1}{R_{2}\left(\frac{C_{2}C_{3}}{C_{2}+C_{3}}\right)}$$

$$\omega_{ZI} = \frac{1}{R_{2}C_{2}}, \quad \omega_{Z2} = \frac{1}{C_{1}(R_{1}+R_{FI})}$$

$$V_{O} \qquad Compensation network$$

$$R_{F1} \qquad R_{1} \qquad R_{2} \qquad C_{3} \qquad C_{2} \qquad V_{C}$$

Figure 3. Type-III compensation circuit.

| $R_{F1}, R_{F2}$      |              | 13 KΩ   | $C_1$           |                             | 1100 pF         |                 |

|-----------------------|--------------|---------|-----------------|-----------------------------|-----------------|-----------------|

| $\mathbf{R}_1$        |              | 566 Ω   | $C_2$           |                             | 510 pF          |                 |

| <b>R</b> <sub>2</sub> |              | 71.5 KΩ | C <sub>3</sub>  |                             | 5.1 pF          |                 |

|                       | Bode Diagram |         |                 |                             |                 |                 |

| Magnitude (dB)        | 60           |         |                 |                             |                 |                 |

|                       | 40           |         |                 | $\wedge$                    |                 |                 |

|                       | 20           |         |                 | $\sim$                      |                 |                 |

|                       | 0            |         |                 |                             |                 |                 |

|                       | -20          |         |                 |                             |                 |                 |

|                       | -40<br>10    | 100     | 1000            | 104                         | 10 <sup>5</sup> | 106             |

| Phase (deg)           | -50          |         |                 | $\cap$                      |                 |                 |

|                       | -100         |         |                 |                             |                 |                 |

|                       | - 150        |         |                 |                             |                 |                 |

|                       | -20010       | 100     | 1000<br>Frequer | 10 <sup>4</sup><br>ncy (Hz) | 10 <sup>5</sup> | 10 <sup>6</sup> |

Table 1. List of components

Capacitors

Parameters

**Resistors** Parameters

Figure 4. Bode plot of the converter's loop gain for  $V_0 = 4$  V and  $I_0 = 1$  A.

From (2), the design values of the compensation network components are calculated and summarized in table 1. The phase margin and gain margin in figure 4 demonstrated a loop gain of converter ~ 59.4 deg at cross frequency 54 KHz and 27 dB at frequency 445 KHz.

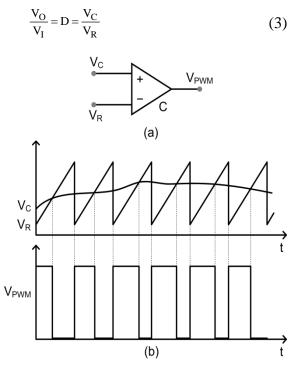

#### 2.2. PWM generator

In figure 5(a), the high-speed comparator is used [14] to provide pulse width modulator (PWM) signals. As mentioned above, the signal  $V_C$  is compared to ramp signal  $V_R$  at fixed amplitude and frequency to produce the pulse signal  $V_{PWM}$  where its duty cycle D is defined as in (3). The waveforms of  $V_C$ ,  $V_R$  and  $V_{PWM}$ are illustrated in figure 5(b). The PWM circuit functions correctly as expected through the loop control and it is able to regulate the output voltage of DC-DC converter.

Figure 5. (a) PWM generation circuit. (b) Corresponding signals.

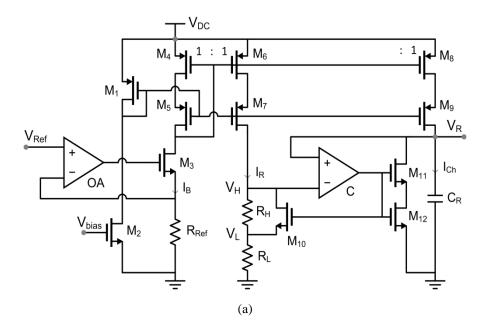

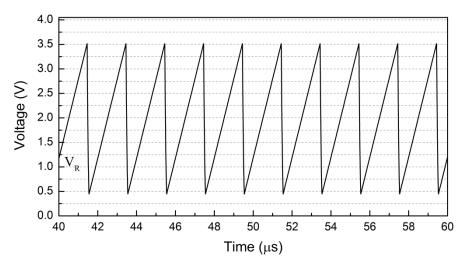

#### 2.3. Ramp generator

The schematic of a ramp generator is shown in figure 6(a). The reference current  $I_B$  is created and controlled by reference voltage  $V_{Ref}$ as a current source. The topology of lowvoltage cascode current mirror is used to create the currents  $I_R$  and  $I_{Ch}$ . The reference voltages  $V_H$  and  $V_L$  are then created by the flow of current  $I_R$  through two resistors  $R_H$  and  $R_L$  in series. The ramp signal is produced by the charging and discharging of the capacitor  $C_R$ . In steady state, when  $V_L < V_R < V_H$ , the transistors  $M_{10} - M_{12}$  are OFF, the reference voltage  $V_H$  is connected to the negative input of the comparator. The capacitor  $C_R$  is then charged during this period until the voltage  $V_R$  is higher than  $V_H$ . That will turn the transistors  $M_{10} - M_{12}$ ON so the reference voltage is switched to  $V_L$ . The capacitor  $C_R$  is discharged rapidly, the voltage  $V_R$  is reduced to a value smaller than  $V_L$  that turn the transistors  $M_{10} - M_{12}$  to OFF state. The process is then repeated. The period of ramp signal is calculated as a function of the charging time ( $T_{rise}$ ) as expressed in equation (4) and the discharging time ( $T_{fall}$ ) of the capacitor  $C_R$ . The ratio of  $T_{fall}/T_{rise}$  is approximately of 5 % that lead to a discharging time  $T_{fall}$  of about 100 ns.

14

$$T_{\text{rise}} = \frac{(V_{\text{H}} - V_{\text{L}})C_{\text{R}}}{I_{\text{Ch}}} = \frac{I_{\text{R}}R_{\text{H}}C_{\text{R}}}{I_{\text{Ch}}} = R_{\text{H}}C_{\text{R}} \qquad (4)$$

As can be seen in equation (4), the value of ramp frequency is a function of  $R_H$  and  $C_R$ . To ensure the performance of ramp generator, a high gain OA [15] with loop gain stability is adopted. The high speed comparator C is designed with a propagation delay of about 10 ns that is suitable for our adaptive-output

converter. Simulations of ramp generator is presented in figure 6(b). It can be seen that ramp signal  $V_R$  meets the maximum value at 3.51 V and minimum value at 0.45 V where the operating signal reaches 500.5 KHz as expected.

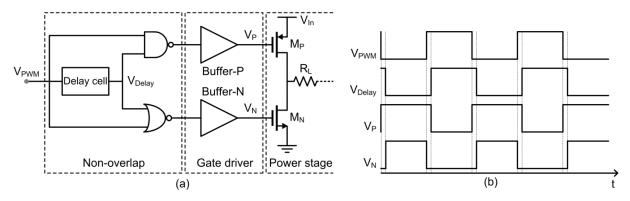

### 2.4. Non-overlap and Gate Driver

The non-overlap and gate driver circuit are illustrated in figure 7(a). The gate driver is a buffer circuit consisting of four inverter layers designed according to the tapering factor in the range of 3 to 4 [14]. The gate driver is used to switch the power transistors  $M_P$  and  $M_N$  of DC-DC converter to obtain a certain output voltage level defined by the duty cycle of switching control signal V<sub>PWM</sub>. In addition, to avoid power loss induced at each switching transition when both  $M_P$  and  $M_N$  are open resulting in shoot-through current loss, the nonoverlap circuit is also implemented. A sufficient small delay between the rise time and fall time of two opposite  $V_P$  and  $V_N$  signals is added. Their waveforms are presented in figure 7(b).

(b)

Figure 6. (a) Ramp generation circuit. (b) Waveform of ramp signal.

Figure 7. (a) Non-overlap and gate driver. (b) Corresponding output waveforms.

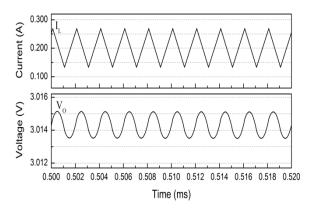

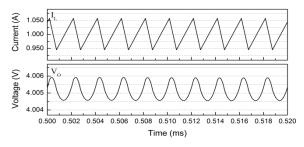

## 3. Simulation results

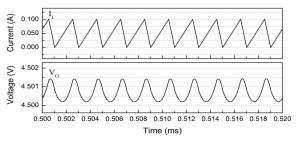

The inductor current and output voltage of the proposed DC-DC converter are shown in figure 8. It is obvious that the continuous conduction mode is guaranteed for three different operation modes of battery charging circuit playing the role as load of the converter. The average inductor current, also called as the load current, reaches the value of 200 mA at output voltage of 3 V, 1000 mA with output voltage of 4 V and 50 mA with output voltage of 4.5 V, respectively. These results confirm that the circuit meets the requirement of power supply for battery charging circuit while it works at trickle charging mode (TC), large current charging mode (LC) and constant voltage charging mode (CV) respectively. Besides, the output voltage ripple is relatively small and almost lower than 1 %.

In figure 9(a), it can be observed that the results show smooth and stable transitions of load current from trickle mode (200 mA) to large current mode (1000 mA) and then to constant voltage mode (50 mA). This current profile meets completely the charging profile of a Li-Ion battery charger. It means that the proposed compensation circuit and the control loop including PWM and gate driver work effectively and guarantee the stability of the

whole system. At light load, when the load current is less than 50 mA, the converter gradually switches to DCM mode, that results in power loss. But this problem can be improved by a detecting-negative-current circuit from the inductor current of the power stage. In addition, a slight undershoot voltage at the transition from trickle to large current mode is also observed in figure 9(b). However, an undershoot voltage of 60 mV which is about 1.8 % of output voltage can be neglected. Interestingly, a constant 0.3 V difference between the output voltage Vo of the proposed DC-DC converter and the battery is recorded for three different charging modes. The converter's output voltage is always 0.3 V higher than the battery voltage. It is seen that Vo is adjusted dynamically according to the battery voltage with the accuracy of over 99 %. As per its name, this DC-DC converter provides an adaptive power supply, not a constant output voltage like any other conventional DC-DC converter, to the battery charger circuit.

16

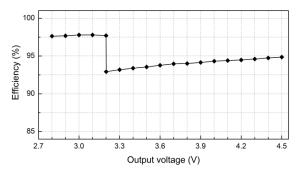

As can be observed in figure 10, the power efficiency of our proposed adaptive-output converter is higher than 94 % for an output voltage varying widely from 2.8V to 4.5 V. The highest efficiency can be reached at 97 % where output voltage varies from 2.8 to 3.2 V and load current is 200 mA. Efficiency is 94 % with an output voltage varying from 3.2 V to 4.5 V where load current is 1000 mA.

(a) Corresponding to TC mode of the battery charger

(b) Corresponding to LC mode of the battery charger

(c) Corresponding to CV mode of the battery charger

Figure 8. Steady-state waveforms of inductor current and output voltage with.

Figure 9. Simulation results of adaptive DC-DC converter with Li-Ion battery charger load. (a) Output current. (b) Output voltage and battery voltage.

Figure 10. Power efficiency of adaptive DC-DC converter with versus output voltage.

## 4. Conclusion

An adaptive and wide-range output DC-DC converter for the Li-Ion battery charger circuit is proposed and designed on the 0.35 µm BCD technology. The converter operating in CCM mode offers a wide range of load current from 50 mA to 1000 mA as well as a broad range of voltage output (from 2.8 to 4.5 V) to the load circuit. The output current and voltage profile of the proposed converter meets perfectly the requirements for Li-Ion battery charger circuit. An average power efficiency of 94 % obtained for the crucial stage of large-current charging mode (1000 mA). As a continuation to our previous work, this circuit helps to complete a charging system from power line DC to a Li-Ion battery by combining with the battery charger in [11].

## Acknowledgements

This research was supported by Prof. Lee Sang-Guk, NICE lab, KAIST, Korea.

## References

D. Linden, and T. B. Reddy, Handbook of batteries, ch. 35, pp. 35.2, New York: McGraw-Hill, 2002.

- [2] S. Dearborn, "Charging Li-Ion batteries for maximum run times," Power Electron. Technol. Mag., pp. 40-49, Apr. 2005.

- [3] A. A. Hussein and I. Batarseh, "A review of charging algorithms for nickel and lithium battery chargers," IEEE Trans. Veh. Tech., vol. 60, no. 3, pp. 830-838, Mar. 2011.

- [4] C.-C. Tsai, C.-Y. Lin, Y.-S. Hwang, W.-T. Lee, T.-Y. Lee, "A multi-mode LDO-Based Li-Ion battery charger in 0.35-mm CMOS technology," IEEE Asia-Pacific Conf. Circuits Syst., 2004, pp. 49-52.

- [5] C. C. Tsai, C. Y. Lin, Y. S. Hwang and T. Y. Lee, "The design of a Li-Ion battery charger based on multimode LDO Technology," Journal of Circuits, Systems and Computers, vol. 18, no. 05, pp. 947-963, 2009.

- [6] Hieu M. Nguyen, Lam D. Pham and Trang Hoang, "A novel Li-Ion battery charger using multi-mode LDO configuration based on 350 nm HV-CMOS," Analog Integrated Circuits and Signal Processing, vol. 88, issue 3, pp. 505-516, Jun. 2016.

- [7] M. Chen and G. A. Rincón-Mora, "Accurate, compact, and power-efficient Li-Ion battery charger circuit," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 11, pp. 1180-1184, Nov. 2006.

- [8] J. Chen, F. Yang, C. Lai, Y. Hwang and R. Lee, "A high-efficiency multimode Li-Ion battery charger with variable current source and controlling previous state supply voltage," IEEE Trans. Ind. Electron., vol. 56, no. 7, pp. 2469-2478, Jul. 2009.

- [9] R. Pagano, M. Baker and R.E. Radke, "A 0.18-µm monolithic Li-Ion battery charger for wireless devices based on partial current sensing and adaptive reference voltage," IEEE J. Solid-State Circuit, vol. 47, no. 6, pp. 1355-1368, Jun. 2012.

- [10] T. C. Huang, R. H. Peng, T. W. Tsai, K. H. Chen and C. L. Wey, "Fast charging and high efficiency switching-based charger with continuous built-in resistance detection and automatic energy deliver control for portable electronics," IEEE Journal of Solid-State Circuits, vol. 49, no. 7, pp. 1580-1594, Jul. 2014.

- [11] H. Nguyen-Van, T. Nguyen, V. Quan, M. Nguyen and L. Pham-Nguyen, "A topology of charging mode control circuit suitable for long-life Li-Ion battery charger," IEEE Sixth International Conference on Communications and Electronics, 2016, pp. 167-171.

18

- [12] Byungcho Choi, Pulsewidth modulated DC-to-DC power conversion: circuits, dynamics, and control designs, John Wiley & Sons, 2013.

- [13] J. Aguado-Ruiz, A. Lopez-Martin, J. Lopez-Lemus and J. Ramirez-Angulo, "Power Efficient Class AB Op-Amps With High and Symmetrical Slew Rate," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 4, pp. 943-947, Apr. 2014.

- [14] Cheung Fai Lee and P. K. T. Mok, "A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique," IEEE Journal of Solid-State Circuits, vol. 39, no. 1, pp. 3-14, Jan. 2004.

- [15] J. Mahattanakul and J. Chutichatuporn, "Design Procedure for Two-Stage CMOS Opamp With Flexible Noise-Power Balancing Scheme," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 8, pp. 1508-1514, Aug. 2005.